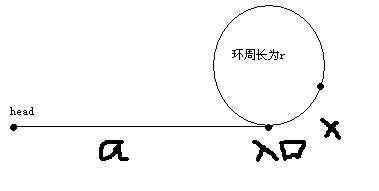

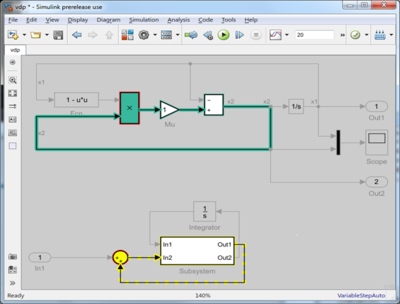

代数环(algebraicloop)发生在两个或多个模块在输入端口具有信号直接传递而形成反馈的情况时,直接传递的模块在不知输入端口的值的情况下无法计算出输出端的值,也就是现在时刻的输出是依赖现在时刻的输入值来计算的。当这种情况出现时simulink会在每一次迭代言算完成时,去决定它是否会有解。代数回路会减缓方真执行的速度并可能会没有解。

添加一个迟滞模块。离散用unit delay,连续用memory,消除代数环。

代数环的涵义好像跟死循环的涵义有点类似,

6.3.1直接馈通模块

在使用Simulink的模块库建立动态系统的模型时,有些系统模块的输入端口(Input ports)具有直接馈通(Directfeedthrough)的特性。所谓模块的直接馈通,是指如果在这些模块的输入端口中没有输入信号,则无法计算此模块的输出信号。换句话说,直接馈通就是模块输出直接依赖于模块的输入。在Simulink中具有直接馈通特性的模块有如下的几种:

(1) Math Function数学函数模块。

(2) Gain增益模块。

(3) Product乘法模块。

(4) State-Space状态空间模块(其中矩阵D不为0)。

(5) Transfer Fcn传递函数模块(分子与分母多项式阶次相同)。

(6) Sum求和模块。

(7) Zero-Pole零极点模块(零点与极点数目相同)。

(8) Integrator积分模块。

在介绍完具有直接馈通特性的系统模块之后,来介绍代数环的产生。系统模型中产生代数环的条件如下:

(1) 具有直接馈通特性的系统模块的输入,直接由此模块的输出来驱动。

(2) 具有直接馈通特性的系统模块的输入,由其它直接馈通模块所构成的反馈回路间接来驱动。

simulink中的代数环中一般有个延迟模块,没有的话也 加个延迟模块,并给延迟模块加初值,就可以解决

爱华网

爱华网