节选自:http://undergraduate.csse.uwa.edu.au/units/600.105/Labs/lab01a.pdf

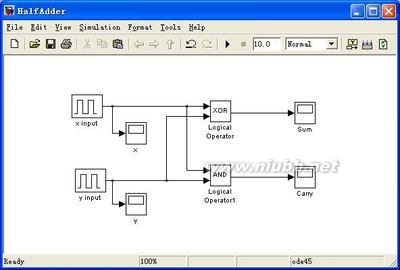

1.构建一个半加器

需要使用导三个库中的模块:LogicalandBitOperations,sources和sinks。让我们先从逻辑门开始。

双击LogicandBitOperations。将LogicalOperator模块拖到工作窗口中,双击模块打开BlockParameters窗口,将Main标签中的Operator选项改为XOR。再拖入一个AND门。

接下来是输入信号。选用PulseGenerator以便检查是否得到了想要的输出。打开Sources面板,拖入两个PulseGenerator并放置再窗口的左侧。

这两个PulseGenerator作为加法器真值表的两个输入。双击第一个并将它的周期(period)设定为4秒,相位延迟(phasedelay)设定为2秒。你可以将这个PulseGenerator重命名为xinput,作为输入的最小标志位(least-significantbit)。双击第二个,将周期设定为8秒,相位设定为4秒,重命名为yinput。

按照上图的方式将输入和两个逻辑门连接起来。将两个Scope连接到PulseGenerator可以检查其输出波形是否是你想要的。打开Sinks面板,拖入两个Scope放到PulseGenerator的旁边,并将两者连接好。双击Scope就可以打开输出波形的窗口。选择Simulation|Start来运行模型,可以看到x和y的信号波形。注意输入向量(yx)在最初的两秒内的数值是00,然后是01,10,11----加法器真值表的数值。现在来检查输出是否是真值表的数值。将Scope与XOR门和AND连接起来,运行仿真,观察输出波形是否和预料一致。是时候保存一下了,时常保存是一个好习惯。2.构建一个全加器按照上述的方法可以很简单的构建一个全加器,如果需要对全加器进行复习,请参考http://www.play-hookey.com/digital/adder.html3.创建子系统选中要创建子系统的模块,选择Edit|CreateSubsystem菜单,创建子系统。这里我们要创建一个全加器,命名为Full_Adder。现在你可以轻松的拷贝粘贴n个全加器来构建一个n位加法器了。4.构建一个4位加法器拖入四个全加器,如图所示连接好,再创建一个子系统,命名为Adder_4bit。5.构建一个16为加法器

拖入四个Adder_4bit,如图所示连接好,再创建一个子系统,命名为Adder_16bit。

爱华网

爱华网