采用FPGA 实现多时钟电路系统时,需要处理不同的钟域之间交换数据的问题,一般接口电路采用异步FIFO ,因此在FPGA 中设计出高效、可靠的异步FIFO 显得尤为重要。作者提出了读写地址增加一位比较的FIFO 设计方案,既可以保证FIFO 高速工作,又可以有效的节省FPGA 的逻辑资源。

1 多时钟系统中的亚稳态

1.1 多时钟系统中亚稳态的产生及危害

当系统中有两个以上的时钟时,电路就是一个异步电路 。如图1 所示,aclk 时钟域的数据adata要传给bclk 时钟域,adata 和abdata 是满足aclk 的建立和保持时间,但是aclk 和bclk 是两个异源时钟,abdata 一定会在某些时刻不满足bclk 的建立和保持时间,即当aclk 和bclk 两个时钟上升沿靠得很近的时,触发器B 的输出abdata 就会出现一个亚稳态,这种状态的电平既不是高电平也不是低电平。

图1 异步时钟引起的亚稳态及危害

亚稳态产生后如果不作处理,直接把信号送到组合电路中,经过布线延迟再经过各种逻辑门将产生不可预知的结果。如图1 所示,bdata 分别经过三个非门本来电平应是一样的,但由于B 触发器输出的亚稳态经过芯片中的布线传输后,到达三个非门再经输出时电平变的各不相同,所以要避免这种错误必须消除亚稳态。

1.2 亚稳态的消除

亚稳态出现后并不会保持很长时间, 对于FPGA 芯片来说一般少于3ns ,之后就是一个非高即低的稳定电平状态。对于工作频率低于几百兆的电路可以在bdata 后再加一个同步到bclk 时钟域的D 触发器,这样得到的输出就是一个稳定的信号。所以为了消除多时钟系统电路中的亚稳态,应在不同时钟域之间加入上面所说的同步模块。如数据要从aclk 时钟域传送到bclk 时钟域中,就要经同步模块同步到时bclk 钟域中去,同样数据要从bclk 时钟域传送到aclk 时钟域中,要经另一个同步模块同步到aclk 时钟域中去。

2 FIFO 在多时钟系统的应用

消除亚稳态只是保证信号电平的稳定,要在不同时钟域中准确传输数据还需要一个接口电路,可以选择握手方式或是FIFO。握手方式由于每传输一个数据都需要各种握手信号,所以不适合实时大量的数据传输, 而采用FIFO 则完全可以胜任。

FIFO 的功能为:在写满标志无效时(为低电平) ,只要写使能信号有效就可以把数据写入FIFO 中,一直到写满它的存储空间为止,这时写满标志为高表明不允许再写;当读空标志无效时,读使能信号有效,数据可以一个一个读出,最先写入的数据最先读出(读出一个数据FIFO 中就少一个) ,直到FIFO 中没有数据为止,此时读空标志有效为高电平,不允许再读。

3 一种新颖的异步FIFO 的实现

3.1 几种FIFO 实现方案的比较

不同的FIFO 主要的区别在于产生满空状态标志逻辑实现的不同,常用的方式有:将读地址和写地址相减来判断FIFO 的满空状态 ;把读、写地址延迟相比较判断FIFO 的满空状态。第一种方案逻辑简单,但电路中的减法器是一个较大的组合电路,它对FIFO 的工作速度产生较大的负面影响。第二种方案的缺点在于,当FIFO 在刚开始工作时没有任何数据,读写地址都是零时,无论延迟哪一个地址再比较结果都为FIFO ,既是满又是空的状态,这显然是一个逻辑错误。

要保证FIFO 的工作速度最好的办法是把读地址和写地址直接比较,不过当读地址和写地址相等时,它可能处于读空状态也可能处于写满状态。要解决这一问题只需要增加一位读写地址,当读写地址完全相等时FIFO 处于读空状态,当最高位不同而其它位地址相同时, 表明写操作赶上读操作,FIFO 处于写满状态。采用这种判断读空写满标志逻辑后,FIFO 既能准确判断出满空状态又能工作到很高的频率。

3.2 异步FIFO 中的其它问题

异步FIFO 处于两个不同时钟域之间,写地址与读地址是两个不同时钟域的数据,在将它们比较前要经过同步。以FIFO 判断写满为例,读地址要被同步到写时钟域中去,再与写地址比较判断是否写满,如果读地址在同步时采用的是二进制,将会产生错误,所以要把它先转换成格雷码。这样当写时钟锁存读地址时,要么是当前的地址要么是前地址。

另外由于比较前要同步,所以当写满标志有效时,FIFO 内其实还可以写入一到两个数据,这一个问题是异步电路本身决定的。读空情况与写满相同。

3.3 FIFO 的功能模块划分和现实

本方案实现的FIFO 数据宽度为8 位,深度为256 ,整个电路分为三个主要功能模如图2 所示,读写地址产生模块,双端口RAM ,满空标志模块。写地址产生模块的功能是,当写能有效且FIFO 写满无效时,写地址增加一,读地址产生模块与之雷同。

双端口RAM 是用来存储数据的,它的读和写是两个独立的过程,互不干扰。满空标志模块用来产生写满、读空标志,该模块的功能还包括实现读写地址的同步比较和二进制与格雷码的转换。设计采用Altera 公司的Acex1k30-144 器件,速度级别为1 ,开发工具是MAX+PLUS II ,硬件描述语言为Verilog HDL 。

图2 FIFO 功能模块的划分

4 设计仿真及总结

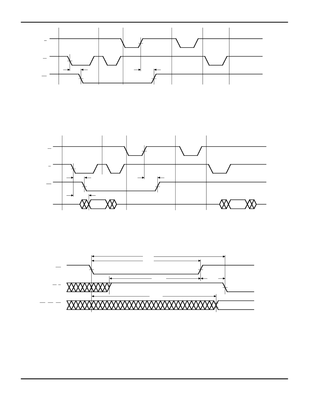

clka、clkb 时钟周期分别为:77 MHz、83 MHz。仿真开始先向FIFO 写入若干个数据,然后读出两个数据,此后只写数据而不读,当双端口RAM 的写地址为2 (FIFO 已被写满) 如图3 所示,写满标志fw马上为高,禁止写数据同时写地址也不再增加,此时将写使能hsa 置低hsb 置高即只读不写,当读地址为2 时( FIFO 已读空) 空标志fr 变高,禁止读并且读地址不再增加,仿真如果如图3 所示。

图3 FIFO 的波形仿真图

最后对电路进行时序分析,得出采用该方案设计的FIFO 工作频率为91.74 MHz (没有对电路优化) ,与文献[2]采用的延迟比较方案工作频率103 MHz相当但不会出现FIFO 刚开始工作时的逻辑错误,而与传统的FIFO 电路77.6 MHz 相比快了不少。

参 考 文 献

[1] Clifford E. Cummings Synthesis and Scripting Techniques for Designing Multi2Asynchronous Clock Designs [ EB/ OL ] . www. fpga.com. cn ,2001.

[2]吴自信,张嗣忠. 异步FIFO 结构及FPGA 设计[J ] . 单片机及嵌入式系统应用,2000 ,22 (3) .

[3 ]赵雅兴. FPGA 原理、设计与应用[M] . 天津:天津大学出版社,1999

爱华网

爱华网