The PWM is based onthe standard Timer block and inheritsall of its features, although only the PWM function ispinned out on the LPC2131/32/34/36/38.【脉宽调制器基于标准的定时器模块并具有其所有特性。】

The Timer is designed to count cycles ofthe peripheral clock(PCLK)【外设时钟】and optionallygenerate interrupts or perform other actionswhen specified timer values occur, based on sevenmatch registers.【定时器对外设始终进行计数,可选择产生中断 或者基于7个寄存器,在到达指定的定时值时,执行其他动作(高/低/翻转/无动作)】

The PWM function is also based onmatch register events【匹配寄存器事件】.

The ability to separately control risingand falling edge locations allow the PWM to be used for moreapplications. For instance, multi-phase【多相位】 motor control typically requires three non-overlapping【无重叠的】 PWM outputs with individual control of all threepulse widths and positions.【而这3个输出的脉宽和位置需要独立进行控制】

Two matchregisters can be used to provide a single edge controlledPWM output.One match register(MR0) controls the PWM cycle rate【PWM周期率】, by resetting the countupon match.The other matchregister(MR1~MR6)controls the PWM edgeposition.

Additional single edge controlled PWMoutputs require only one match register each, since the repetition 【重复】 rate is the samefor all PWM outputs. Multiple single edge controlled PWM outputswill all have a rising edge at the beginning of each PWM cycle,whenan MR0 match occurs.

Three match registers can be used toprovide a PWM output with both edgescontrolled.【3个匹配寄存器共同控制一个 双边沿PWM输出】Again, the MR0 matchregister controls the PWM cycle rate. Theother match registers control the two PWM edge position.Additional double edge controlled PWM outputs require only twomatch register each, since the repetition rate is the same for allPWM outputs.

With double edge controlled PWM outputs,specific match registers control the rising and falling edge ofoutput. This allows both positive going PWMpulses【正脉冲】(when the rising edgeoccurs prior to the falling edge),and negativegoing PWM pulses【负脉冲】(when the falling edge occurs prior to the risingedge).

May be used as a standardtimer if the PWM mode is not enabled.

寄存器

PWMIR--中断寄存器包含11个位,其中7个位用于匹配中断,4个位保留。如果有中断产生,PWMIR对应位置位。向对应位的IR写入1,会置位中断,写入0,无效。位:10 98 76 54 32 10PWMMR6中断 54 保留 3 21PWMMR0中断

PWMTCR--定时器控制寄存器control the operation of the PWM Timercounter.【控制PWM定时器计数器的操作】位:3 2 1 0PWM使能 保留 计数器复位 计数器使能|只有在PWMLER中的 |为1时,PWMTC和 |为1时,PWMTC和|相应位置位后 |PWMPC在pclk的 |PWMPC使能计数|发生的匹配0事件, |下一个上升沿 |C为0时,|才会使程序写入 |同步复位。该位为 |计数器被禁止|匹配寄存器的值生效。 |0之前,保持复位状态 |

PWMTC--定时器计数器PWM Timer Counter is incremented whenthe PC reaches its terminal count.

Unless it is reset before reaching itsupper limit, the PWMTC will count up through the value 0xFFFF,FFFFand then warp back to the value 0x0000,0000.

This event does not cause an interrupt,but a match register can be used to detect an overflow ifneeded.

PWMPR--预分频寄存器specifies the maximum value for thePWMPC.

PWMPC--预分频计数器PC每个周期+1,其值达到PWMPR中的值时,PWMPC+1,on thenext pclk->reset PWMPC

PWMMR0~PWMMR6--匹配寄存器continuously compared to th PWMTC value.TC一直增加,当两个值相等时,触发动作(产生中断、复位计数器、停止定时器),具体执行什么动作由PWMMCR控制。

PWMMCR--匹配控制寄存器控制在发生匹配时所执行的操作。位: 20:18 17:15 14:12 11:9 8:6 5:3 2:0对应于:PWMMR6 PWMMR5PWMMR4PWMMR3PWMMR2PWMMR1PWMMR0 | | 位14 13 12 值 1 1 1PWMMR4与 |停止 |复位 |产生PWMTC值匹配|PWMTC和 |PWMTC |中断 |PWMPC, | |PWMTCR[0] |复位为0

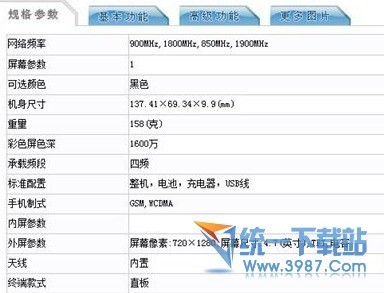

PWMPCR--控制寄存器enable and select the type of each PWMchannel

位:15 14 13 12 11 109 8 7 6 5 4 32 10保留PWMENA6 5 43 21 保留 PWMSEL6 5 43 2 保留 0 禁止输出 1双边沿控制模式 1 使能输出 0单边沿控制模式

PWMLER--锁存使能寄存器control the update of the PWMMR0~PWMMR6when they are used for PWM gegeration.位:7 6 5 4 3 21 保留 PWMMR6锁存 5 4 3 21

Rules for Single Edge Controlled PWMOutputs1.All single edgecontrolled PWM outputs go high at the beginning of a PWM cycleunless their match value is equal to0.2.Each PWM output will go lowwhen its match value is reached.if no match occurs(i.e. the matchvalue is greater than the PWM rate),the PWM output remainscontinuously high.单边沿控制的 PWM 输出规则⑴所有但边沿控制的 PWM 输出在 PWM周期开始时都为高电平,除非它们的匹配值等于0.⑵每个PWM输出在到达其匹配值时都会变为低电平。如果没有发生匹配,PWM将一直保持高电平。

爱华网

爱华网