How Controllers Maximize SSD Life

neeyuese 翻译于 2014-1-1320:59

原文下载:http://www.snia.org/sites/default/files/SSSITECHNOTES_HowControllersMaximizeSSDLife.pdf

现在的MLC颗粒P/E基本上是3000~10000附近,随着制程进一步提高,未来会跌到1000~1500。如何通过主控最大限度的提高整个SSD的寿命呢?

这点写入量对消费级产品来说无伤大雅,但是对企业级产品来说问题越来越严峻,毕竟MLC颗粒已经正式进入企业级市场不少时间了,而且大有取代昂贵的SLC颗粒地位的趋势。

既然大家都用着一样制程的颗粒,为何有些厂牌标称的SSD写入耐久度那么高,而有些却又很普通呢?

那是因为主控算法架构带来的明显区别,本文会讲一下SSD主控提升耐久度的8个秘密。

1.磨损均衡 - Wear Leveling

2.外部数据缓冲 -External Data Buffering

3.改进的ECC -Improved ECC

4.错误管理技术 -Error Management

5.降低写入放大 -Reduced Write Amplification

6.提升预留空间 -Over Provisioning

7.闪存区块磨损反馈 -Feedback on Block Wear

8.闪存的内部管理 -Internal NAND Management

任何主控只要做好了上面的8点,即可大幅度的提升SSD的寿命,用3000P/E的MLC颗粒做出的SSD产品跑出平均3~5万P/E也不在话下,当然没有厂商会用颗粒耐久度标称自己SSD的产品,只会写多少TB,甚至PB的耐久度。

1. 磨损均衡是如何帮助主控提高SSD耐久度的。

闪存寿命是以P/E次数来计算的,而磨损均衡就是确保闪存内每个块被写入的次数相等的一种机制。当数据试图写入到某个块之前,它会自动被迫写入到另外的块内来保证磨损的均衡。每个厂商的磨损均衡算法都不同,总有一些做的比别人更好。

有两种基本类型的磨损均衡:静态和动态。动态磨损均衡只会处理正在变化的和未使用的数据区域,而不会去处理已有数据的区域。静态磨损均衡会在发觉已有数据的区域磨损度数明显小于平均磨损度时候对它们进行搬运操作来达到磨损均衡。这两种磨损均衡的执行范围也有讲究,有全局磨损均衡和局部磨损均衡,全局磨损均衡观察整块SSD的磨损度操作,而局部磨损均衡则针对特定区域范围进行操作。当然磨损均衡的操作特别是全局静态磨损均衡由于需要来回移动数据,会增加不必要的写入,这中间如何折中考虑则需要看SSD的设计师对主控内部的管理算法独特的理解,好的算法取决于许多变量,例如闪存的类型,工作量和速度等要求。

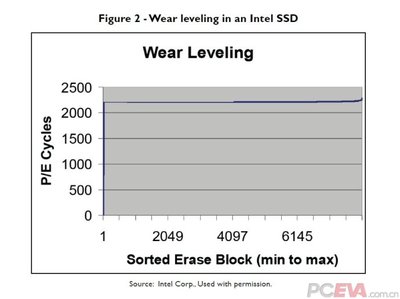

上面是Intel给出的2个例子,前一个图磨损最大值比平均值相差近3倍(早期SSD主控),后者最大值和最小值只相差4%。(初代和二代Intel主控)很明显Intel使用的磨损均衡算法在这里表现更好了,相应的能够更多的利用到所有颗粒的耐久度达到提高整块SSD耐久度的目的。

2. 外部数据缓冲是如何帮助主控提高SSD耐久度的。

外部数据缓冲用来缓存闪存数据,减少闪存的磨损度。不管是主控内部的缓存还是外部缓存,都有很多使用方式来降低闪存磨损度。其中最常见的就是合并写入,把许多零碎的小文件在缓冲区内合并再一起写入闪存,能够大幅度的提升写入速度和降低写放大。举个例子:如果SSD在写入时候没有使用缓冲区,当写入许多小文件,之后的文件写入可能因为之前的文件已经写入进同一个闪存介质而需要把它们同时再搬运到另一个闪存块中,无谓增加了操作时间和浪费了P/E。外部数据缓冲的优势除了合并写入外,还可以用来做“覆盖写入”,比如把原本需要大量写到同一个地址的数据在缓冲区内“覆盖”操作,直到最后才写入到闪存上,大幅度降低了闪存的写放大,外部数据缓冲区一般很小,一般在2MB以内,取决于主控算法的设计需求。当然外部数据缓冲区有掉电数据丢失的隐患,所以需要靠掉电保护来保证数据的完整性。

3. 改进的ECC是如何帮助主控提高SSD耐久度的。

ECC的强度是影响SSD耐久度的一个关键因素,所有的闪存都需要ECC纠错,这些错误是随机产生的,我们一般叫做“软错误”,因为闪存芯片内部的噪声非常大,传输时候的信号强度较弱,这也是为何闪存是当今最便宜的存储记忆体的道理。另外随着闪存的磨损,出错率会越来越高,这是因为某些bit会永远卡在一个状态下,我们称作“硬错误”。因此不难理解,闪存的耐久度取决于大量磨损后"硬错误”大量增加导致无法纠错,如果提高ECC能力,自然也就能尽可能晚的出现这种情况。当然有时候人品不好“软错误”忽然大量增加导致突破ECC能力的情况也会发生,但是那个不应该会对全局耐久度产生大影响,只是会出现几个重映射而已。

举例子吧,让我假设某个全新的闪存芯片软错误是8bit的ECC需求,这个意思是每个Page在读取时可能会随机出现不大于8bit的软错误(通常就是芯片噪声导致),如果主控的ECC能够纠错12bit的话,那么就是说除非这颗闪存芯片P/E磨损到至少5个bit的硬错误再加上8bit的软错误,才会导致ECC无法纠错重映射的情况发生。现在让我们说如果闪存厂保证出现5bit硬错误的情况是需要P/E磨损达到10000(或者5000,或者3000...)才会出现,那么我们就说在这个ECC能力下,这个产品可以做到xxxP/E的指标,如果把ECC能力提高到20bit纠错就能达到更多的P/E要求。

当然提高主控ECC纠错强度的代价是价格的大幅度提高,更强力的ECC需要更多的功耗,计算资源,更复杂的架构设计,更多的内存容量,同时降低了SSD的性能。ECC的架构同时也是数学家们一直研究的项目,如何牺牲最小的资源来达到优秀纠错能力,这绝对不是随便就能做好的。LDPC将成为下一代SSD的标配ECC算法,当然如果没有相关技术经验积累的话,反而会得不偿失的,传统机械硬盘控制器芯片制造厂商这时候就要开心的笑了。

4. 错误管理技术是如何帮助主控提高SSD耐久度的。

前面说的ECC是纠错能力,那么这里说的错误管理技术则指的是错误过滤能力(降低出错率)。聪明的朋友应该知道我要说的是什么了,他就是DSP数字信号处理。DSP能够过滤闪存芯片产生的软错误,这些软错误主要是因为闪存芯片内部干扰产生。

解释下吧,闪存芯片内部每个存储单元状态的变化会对相邻的存储单元状态产生细小干扰,例如你对这个存储单元放电,旁边的单元其实也会放电,如果是充电,旁边的单元也会充电,只是这个值会很弱,但是一旦积累到一定值后状态就变化了,这个就叫闪存的读写干扰。以前我说过取决于闪存芯片的品质,同一个区域读取几百次后,就要把这个区域的数据移动到别处,不然会出现错误,因此闪存的读取次数也并非无限大的,只是相比写入磨损来说小得多。

数字信号处理引擎知道闪存中哪个存储单元会干扰另外的存储单元,通过把原本的数据重新编码后变成特定不易干扰的"符号"写入来降低干扰的程度,由于这些"符号"也需要时间处理,因此会降低写入速度。当读取这些闪存区域时,这些"符号"重编码成实际的数据,大幅度降低了出错率,再进入ECC引擎纠错。因此可以把数字信号处理理解成一个过滤处理,大幅度降低了软错误的数量,达到大幅度增加耐久度的目的。数字信号处理在当前的SSD中并没有非常广泛的应用,但是随着闪存工艺的提升,这是必须要使用到的技术之一。

5. 降低写入放大是如何帮助主控提高SSD耐久度的。

写放大成为了当前SSD主控算法研究的重点之一,低写放大不但能够大幅度提升SSD寿命同时保持高性能。由于闪存的特性导致读写和擦除单位不等,因此闪存主控需要自己对内部数据结构进行管理和优化,而这部分操作并非主机的请求,导致了主机请求的写入量和闪存实际写入量出现了差距,造成了写放大。某些主控支持数据的压缩处理,能够降低闪存中数据的写入量,在一些特定的情况下写放大也就能降低到1以下。如果把写入同一地址的数据在数据缓冲区里就覆盖掉,也能降低一定的写入放大。不管如何,通过SSD的算法设计,尽可能的降低写入放大能够降低闪存的磨损度来达到耐久度提升的目的

6. 提升预留空间是如何帮助主控提高SSD耐久度的。

预留空间的多少也是影响SSD耐久度的关键因素之一,因为它帮助SSD主控降低了写放大。预留空间能够提高多少SSD耐久度呢?根据相关数据表明,如果一款SSD的算法设计到位,使用MLC闪存的话,45%预留空间的SSD相比20%预留空间的SSD耐久度多2倍,而75%则提高到3倍,100%预留空间则接近4倍,提高到250%的话则是6倍。许多消费级的SSD产品只有7%的预留空间,相比20%的预留空间耐久度会少3倍。

7. 闪存区块磨损反馈是如何帮助主控提高SSD耐久度的。

SSD主控通过区块磨损反馈能够得知现在操作的闪存的磨损度到底如何,这个技术在目前的SSD中使用的极少,但却是个趋势。我们都知道闪存制造商定义了颗粒耐久度3000,5000或者10000次等,那么现在的问题是如果P/E超过这个数字后会如何?根据SNIA一份报告显示,Fusion-IO的某款采用SLC的产品,达到了200~400万P/E才出现大量错误,但是闪存制造商只标称10万次。

既然闪存能够写入和擦除那么多次,为何闪存制造商不标称高点呢?这样不是能够带来更大的市场竞争力么?实际上闪存制造商并没有去测,特别是消费级产品市场上,大量的证据表明过高的标称值并不能卖出更多的闪存芯片,相反要去验证实际颗粒耐久度的花费是无法估量的,同时耐久度测试也毁了测试的芯片。由于耐久度会因为生产晶圆批次品质的不同而出现大幅度的变化,制造商不可能花费大量的精力去测试每个批次的耐久度,即使能够这样做(测试每个批次耐久度花去大量时间),也会导致产品发货日期的大幅度推迟。因此正确的做法是设置一个最低标称值,就算最烂的合格颗粒也能通过的标准。

既然如此,闪存区块磨损反馈的技术就能起到作用了,SSD主控可以通过颗粒的擦写反馈信号得知当前颗粒的磨损状态,再结合磨损平衡算法针对这些颗粒进行进一步的耐久度挖掘。说的简单点就是不支持这个技术的主控会对每个颗粒进行完全平衡的磨损例如统一3000次,而支持此技术的主控通过颗粒反馈的出错率和信号状态来判断每个颗粒的耐久度临界点而进行更进一步的耐久度挖掘。

8. 闪存的内部管理是如何帮助主控提高SSD耐久度的。

上面7点感觉已经把闪存的耐久度挖掘到极限了,难道还有更狠的?是的,没有比闪存制造商更了解自己的产品了。只看制造商给出的标准数据手册做出的产品怎么可能比的过拥有内部参数的高级版数据手册呢?除非你和制造商的关系很铁,或者你有足够的理由让它们相信你即使放弃更有价格竞争力的别家颗粒,也只使用它们的颗粒开发产品。市场上做SSD的那么多,一般很难让它们注意到你,拿到了这款颗粒的内部参数,对设计产品将获得巨大的帮助,这些参数对SSD耐久度会起到至关重要的作用。

爱华网

爱华网