第一章设计指标…………………………………….... |

第一章:设计指标

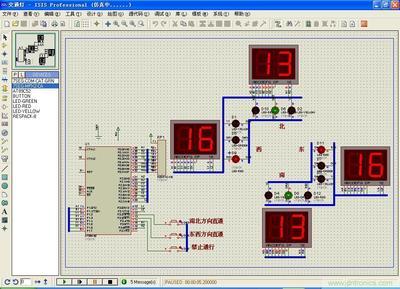

要求一:设计一个十字路口交通灯控制电路,要求东西南北两条主干道红绿黄灯变化如表一所示,并以倒计时方式指示干道通行或禁止的维持时间;

要求二:在东西南北主干道的基础上加上转弯灯,要求东西走完22s后,东西方向转弯灯绿灯亮7s黄灯亮3s,然后进入南北主干道16s,结束后南北转弯灯绿灯亮7s黄灯亮3s,如此循环;如表二所示

系统硬件要求:设计的控制部分以FPGA实现,用发光二极管模拟东西南北主干道及转弯灯,用七段共阴显示干道通行时间,用74190实现22/16或者32/26的翻转,用7485实现数据比较,用7490实现分频设计,并且完成动态扫描,用74153实现数据的选择输出,从而控制七段共阴显示器;

第二章系统概述

2.1设计思想

根据表一得到东西南北主干道的状态图:

图一

由图所示可知,各状态持续时间有所不同,所以电路的核心控制部分为状态机和计数器。

1.状态定时的设计

74190的介绍:U/D是加减计数控制端;CT是使能端;LD是异步置数控制端;D0~D3是并行数据输入端;Q0~Q3是计数器状态输出端;CO/BO是进位借位信号输出端;RC是多个芯片级联时级间串行计数使能端,CT=0,CO/BO=1时,RC=CP,由RC端产生的输出进位脉冲的波形与输入计数脉冲的波形相同。(U/D即为课本的DNUP,CT为GN,LD为LDN,CP为CLK)

各信号的时序关系如果所示:

Di(22)D7D6D5D4D3D2D1D0=00100010

Dj(16)D7D6D5D4D3D2D1D0=00010110

对比可知,D7D6D3D0置零D2置1,D5D4D2随状态不同不同,由状态电平S确定。当电路处于i状态时定时器的预置数是控制j状态的定时值,D5D4D2=011;当电路处于J状态时定时器的预置数是控制I状态的定时值,D5D4D2=100;显然,采用一个反向综合触发器的输出即可控制定时计数器的预置控制逻辑。

根据时序逻辑图,用高位MAXMIN端经过非门控制T’触发器的脉冲输入端控制状态S,用两片74090的MAXMIN经过与非门控制预置数端,

仿真波形如图所示:

状态定时控制的电路如图所示:

BCD COUNTER |

LDN |

A |

C |

B |

D |

GN |

CLK |

DNUP |

QA |

QB |

QD |

QC |

MXMN |

RCON |

74190 |

inst |

BCD COUNTER |

LDN |

A |

C |

B |

D |

GN |

CLK |

DNUP |

QA |

QB |

QD |

QC |

MXMN |

RCON |

74190 |

inst1 |

NOT |

inst3 |

PRN |

CLRN |

T |

Q |

TFF |

inst9 |

VCC |

NAND2 |

inst7 |

NOT |

inst12 |

, |

1 |

2 |

3 |

4 |

5 |

6 |

7 |

GND |

VCC |

VCC |

pin_name |

INPUT |

0 |

d7 |

OUTPUT |

d6 |

OUTPUT |

d5 |

OUTPUT |

d4 |

OUTPUT |

d3 |

OUTPUT |

d2 |

OUTPUT |

d1 |

OUTPUT |

d0 |

OUTPUT |

s |

OUTPUT |

data_in[0] |

2,脉冲分频设置

脉冲发生器为整个系统提供驱动,将输入端分配给FPGA实验板的PIN55引脚,则会由实验板上产生频率为10 MHz的输入脉冲,用7片7490,每一级都构成10分频电路,使频率从10 MHz降低为1Hz,具体电路如下图所示。

2.时间显示

两位动态扫描电路

通过四片74153数据选择器(小数点在此不用,不作说明)作为数据输入,通过上面设计的分频器产生的1KHZ信号控制选择输出,,并且通过74138选择七段共阴显示器亮,七段共阴显示器的位置和DE1DE2DE3有关

DE3 | DE2 | DE1 | C1~C6 |

0 | 0 | 0 | C1 |

0 | 0 | 1 | C2 |

0 | 1 | 0 | C3 |

0 | 1 | 1 | C4 |

1 | 0 | 0 | C5 |

1 | 0 | 1 | C6 |

两位动态扫描为正确显示时间,用ADHL文件编译真值表如下:

SUBDESIGN7segl

(

data_in[7..4]:INPUT;

a,b,c,d,e,f,g:OUTPUT;

)

BEGIN

TABLE

data_in[7..4]=> a,b,c,d,e,f,g;

b"0000"=> 1,1,1,1,1,1,0;

b"0001"=> 0,1,1,0,0,0,0;

b"0010"=> 1,1,0,1,1,0,1;

b"0011"=> 1,1,1,1,0,0,1;

b"0100"=> 0,1,1,0,0,1,1;

b"0101"=> 1,0,1,1,0,1,1;

b"0110"=> 1,0,1,1,1,1,1;

b"0111"=> 1,1,1,0,0,0,0;

b"1000"=> 1,1,1,1,1,1,1;

b"1001"=> 1,1,1,0,0,1,1;

b"1010"=> 1,1,1,0,1,1,1;

b"1011"=> 0,0,1,1,1,1,1;

b"1100"=> 1,0,0,1,1,1,0;

b"1101"=> 0,1,1,1,1,0,1;

b"1110"=> 1,0,0,1,1,1,1;

b"1111"=> 1,0,0,0,1,1,1;

END TABLE;

END;

打包后的文件如图:

动态扫描电路图,如果所示:

4,组合逻辑控制

模块将状态定时模块输出的时间与时间节点进行比较,从而确定电路处于22 s或者16 s的具体的某个状态。由表1可知,东西(I)或南北(J)的控制状态都有3个阶段的控制逻辑,分别对应3个时间段:1~3 s,4~6 s和大于6 s,因此,采用数字比较器进行比较,确定定时值小于4 s或大于6 s,方法如图7所示,采用4片7485数字比较器,两两级联,其中一个由状态定时模块的输出与4即二进制0100比较;另一个由状态定时模块的输出与6即二进制0110比较。数值比较器的电路图如图所示:

编写组合逻辑真值表,将状态信号S,两个数字比较器的输出Y1,Y2和1 Hz脉冲作为输入,各个灯的状态作为输出。从而根据逻辑关系得出对应时间电路的状态,控制红、黄、绿灯处于不同的状态。S判断电路处于22 s状态还是16 s状态,Y1,Y2区分东西、南北六个阶段状态,1 Hz脉冲实现绿灯闪烁。

SUBDESIGNRYG

(

data_in[3..0]:INPUT;

ER,EY,EG,SR,SY,SG:OUTPUT;

)

BEGIN

TABLE

data_in[3..0]=>ER,EY,EG,SR,SY,SG;

b"0011"=> 0,0,1,1,0,0;

b"1011"=> 0,0,1,1,0,0;

b"0001"=> 0,0,0,1,0,0;

b"1001"=> 0,0,1,1,0,0;

b"0101"=> 0,1,0,1,1,0;

b"1101"=> 0,1,0,1,1,0;

b"0010"=> 1,0,0,0,0,1;

b"1010"=> 1,0,0,0,0,1;

b"0000"=> 1,0,0,0,0,0;

b"1000"=> 1,0,0,0,0,1;

b"0100"=> 1,1,0,0,1,0;

b"1100"=> 1,1,0,0,1,0;

END TABLE;

END;

至此交通灯南北主干道的电路模块设计完成。

2.2总体工作过程介绍

状态定时用来实现22/16循环,并且减计数过程输出的D7D6D5D4D3D2D1D0输入到动态扫描电路,把数字显示在七段共阴显示器上,此外输出的数字经过数值比较器产生控制端Y1Y2与S,CLK,一起通过组合逻辑控制,控制东西南北主干道的红黄绿灯的状态变化。

二:加上转弯灯之后电路设计过程

设计思路和主干道基本一致,转弯控制位32/26循环,预置数发生改变,其次,数字比较器部分要和16,14,10,4进行比较,组合逻辑控制的ADHL文件也需要修改;各部电路图如下所示

状态定时电路图:

数值比较电路图:

组合逻辑控制ADHL真值表:

SUBDESIGNlight

(

data_in[5..0]:INPUT;

er,ey,eg,etr,ety,etg,sr,sy,sg,str,sty,stg:OUTPUT;

)

BEGIN

TABLE

data_in[5..0] =>er,ey,eg,etr,ety,etg,sr,sy,sg,str,sty,stg;

b"011010"=> 1,0,0,1,0,0,0,0,1,1,0,0;

b"111010"=> 1,0,0,1,0,0,0,0,1,1,0,0;

b"010010"=> 1,0,0,1,0,0,0,0,0,1,0,0;

b"110010"=> 1,0,0,1,0,0,0,0,1,1,0,0;

b"010110"=> 1,1,0,1,0,0,0,1,0,0,0,0;

b"110110"=> 1,1,0,1,0,0,0,1,0,0,0,0;

b"010100"=> 1,0,0,1,0,0,1,0,0,0,0,1;

b"110100"=> 1,0,0,1,0,0,1,0,0,0,0,1;

b"010101"=> 1,0,0,1,0,0,1,0,0,0,1,0;

b"110101"=> 1,0,0,1,0,0,1,0,0,0,1,0;

b"001010"=> 0,0,1,1,0,0,1,0,0,1,0,0;

b"101010"=> 0,0,1,1,0,0,1,0,0,1,0,0;

b"000010"=> 0,0,0,1,0,0,1,0,0,1,0,0;

b"100010"=> 0,0,1,1,0,0,1,0,0,1,0,0;

b"000110"=> 0,1,0,0,0,0,1,1,0,1,0,0;

b"100110"=> 0,1,0,0,0,0,1,1,0,1,0,0;

b"000100"=> 1,0,0,0,0,1,1,0,0,1,0,0;

b"100100"=> 1,0,0,0,0,1,1,0,0,1,0,0;

b"000101"=> 1,0,0,0,1,0,1,0,0,1,0,0;

b"100101"=> 1,0,0,0,1,0,1,0,0,1,0,0;

END TABLE;

END;

第三章:电路的组构和调试:

电路中遇到的重要问题:

1.cannotbe assigned more than one value同一个点被接入了不同的值,这个问题一般是电路连接问题或者电路中不该出现节点的地方出现了节点。

2.No exact pin location assignment(s)for 16 pins of 16 total pins定义的管脚没有和外部管脚连接

3.Following 9 pins have nothing, GND,or VCC driving datain port -- changes to this connectivity maychange fitting results

有九个管脚悬空或接地或接电源

4.Can't compile duplicate declarationsof entity "count3" into library "work"

原理图文件和图中一个器件的名字重复,修改一下原理图文件名即可

5.Can'tcontinue timing simulation because delay

annotationinformation for design is missing. 如果只需

要进行功能 仿真,不全编译也是可以进行下去的,

但时序仿真就必须进行全编

(即工具栏上的紫色实心三角符号那 项)

6.Can't find signal in vector sourcefile for input pin

|wh ole|clk10m

波形仿真文件( vector source file)中并没有把所有的

输入信号(input pin)加进去, 对于每一个输入都需要有激

励源的

7.Warning: Pin "s" is missingsource

引脚s没有接入

8.Error: Port "100HZ" does not exist inmacrofunction

"inst13"

源文件已被损坏,造成打包出来的模块运行时打包文件不可

用。

第五章结束语

经过两个星期在实验室的学习,在老师们的悉心指导和严格要求下,我终于完成了《基于FPGA的交通灯数字电路设计》

从模块分析到模块设计到具体分析仿真,每一步都需要我们认真面对,考虑模块的局部性还要考虑电路的全局性,分析交通灯电路的要求,我们需要掌握需要什么器件什么逻辑,除了掌握数电课本上的基本知识。我们还需要对quartus 2的基本操作有一定的了解。

在具体的设计过程中,我遇到的问题远比我想象中的大得多,在不断的仿真验证分析,找出错误改正错误,这样一步步循环,我的课设电路差不多有了一个雏形,这样一天几个小时呆在实验室感觉蛮充实的,当电路运行成功后蛮有成就感的,现在回想一下,我是实实在在走过了一个完整的课设过程并且享受了这一过程,我的实验总结就此结束。

“只有经过长时间完成其发展的艰苦工作,并长期埋头沉浸于其中的任务,方可望有所成就。”

黑格尔

交通灯电路图

PIN_55 |

VCC |

cp |

INPUT |

PIN_7 |

ER |

OUTPUT |

PIN_8 |

EY |

OUTPUT |

PIN_9 |

EG |

OUTPUT |

PIN_10 |

SR |

OUTPUT |

PIN_11 |

SY |

OUTPUT |

PIN_12 |

SG |

OUTPUT |

PIN_141 |

acom |

OUTPUT |

PIN_33 |

de1 |

OUTPUT |

PIN_36 |

de2 |

OUTPUT |

PIN_37 |

de3 |

OUTPUT |

PIN_23 |

a |

OUTPUT |

PIN_26 |

b |

OUTPUT |

PIN_27 |

c |

OUTPUT |

PIN_28 |

d |

OUTPUT |

PIN_29 |

e |

OUTPUT |

PIN_30 |

f |

OUTPUT |

PIN_31 |

g |

OUTPUT |

10M |

1M |

100KHz |

10KHz |

1KHz |

100Hz |

10Hz |

1Hz |

fpq |

inst2 |

data_in[3..0] |

ER |

EY |

EG |

SR |

SY |

SG |

ZH |

inst4 |

VCC |

MULTIPLEXER |

1C1 |

1GN |

1C0 |

2C0 |

2GN |

2C2 |

1C2 |

1C3 |

B |

A |

2C1 |

2C3 |

1Y |

2Y |

74153 |

inst18 |

MULTIPLEXER |

1C1 |

1GN |

1C0 |

2C0 |

2GN |

2C2 |

1C2 |

1C3 |

B |

A |

2C1 |

2C3 |

1Y |

2Y |

74153 |

inst19 |

GND |

GND |

GND |

COMPARATOR |

A3 |

B2 |

A2 |

AEBI |

AGBI |

ALBI |

A0 |

B0 |

B3 |

A1 |

B1 |

ALBO |

AGBO |

AEBO |

7485 |

inst28 |

COMPARATOR |

A3 |

B2 |

A2 |

AEBI |

AGBI |

ALBI |

A0 |

B0 |

B3 |

A1 |

B1 |

ALBO |

AGBO |

AEBO |

7485 |

inst1 |

COMPARATOR |

A3 |

B2 |

A2 |

AEBI |

AGBI |

ALBI |

A0 |

B0 |

B3 |

A1 |

B1 |

ALBO |

AGBO |

AEBO |

7485 |

inst3 |

COMPARATOR |

A3 |

B2 |

A2 |

AEBI |

AGBI |

ALBI |

A0 |

B0 |

B3 |

A1 |

B1 |

ALBO |

AGBO |

AEBO |

7485 |

inst5 |

GND |

VCC |

GND |

CP |

Q0 |

Q1 |

Q2 |

Q3 |

Q4 |

Q5 |

Q6 |

Q7 |

S |

jtd |

inst |

data_in[7..4] |

a |

b |

c |

d |

e |

f |

g |

7segll |

inst30 |

7 |

6 |

2 |

5 |

1 |

4 |

0 |

data_in[3..0] |

data_in[7] |

data_in[6] |

data_in[5] |

3 |

data_in[7..4] |

data_in[4] |

7 |

6 |

5 |

4 |

3 |

2 |

1 |

0 |

0 |

1 |

3 |

2 |

6 |

7 |

4 |

5 |

data_in[2] |

data_in[1] |

0 |

1 |

2 |

3 |

4 |

5 |

7 |

6 |

data_in[0] |

data_in[3] |

交通灯(带转弯)电路图

参考文献:《数字电路及系统设计》赵曙光 刘玉英 崔葛瑾主编

基于FPGA的数字电路系统设计崔葛瑾主编

及相关ppt,资料等

爱华网

爱华网