实验一QuartusII的VHDL输入设计

---应用QuartusII完成基本时序电路的设计

姓名:李静学号:1023019857 日期:2013-05-22

(一)实验目的:

熟悉QuartusⅡ的VHDL文本设计过程,学习简单时序电路的设计、仿真和测试。

(二)实验仪器:

计算机一台,ALTERA公司Cyclone系列的EP1C3TC144芯片实验箱。

(三)实验原理:

对于异步清零和同步加载与时钟使能的计数器:当时钟信号CLK、复位信号RST、时钟使能信号EN或加载信号LOAD中任一信号发生变化,都将启动进程。此时如果RST为‘0’,将计数器清零,该操作独立于CLK,如果RST为‘1’,则看是否有时钟信号的上升沿,如果有且EN=‘1’,接下去是判断加载控制信号LOAD的电平,如果LOAD为低电平,则允许将输入口的四位加载数据置入计数器中,以便计数器在此基础上累计计数。如果LOAD为高电平,则允许计数器计数;此时若数值小于9,计数器将进行正常计数,否则计数器清零。但如果EN=‘0’,则计数器保持原值不变。

(四)实验内容:

设计含异步清零和同步加载与时钟使能的计数器(使用例3-20),给出程序设计、软件编译、仿真分析、硬件测试及详细实验过程。

实验程序:

【例3一20】:

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY CNT10 IS

PORT (CLK,RST,EN,LOAD : IN STD_LOGIC;

DATA : IN STD_LOGIC_VECTOR(3 DOWNTO 0);

DOUT : OUT STD_LOGIC_VECTOR(3 DOWNTO0);

COUT : OUT STD_LOGIC);

END CNT10;

ARCHITECTURE behav OF CNT10 IS

BEGIN

PROCESS(CLK, RST,EN,LOAD)

VARIABLE Q : STD_LOGIC_VECTOR(3 DOWNTO 0);

BEGIN

IF RST = '1' THEN Q:= (OTHERS=>'0') ;--计数器异步复位

ELSIF CLK'EVENT AND CLK='1'THEN--检测时钟上升沿

IF EN = '1'THEN--检测是否允许计数(同步使能)

IF LOAD = '0' THEN Q:=DATA;ELSE --由LOAD='0'装载新数据

IF Q < 9 THEN Q:= Q + 1;--允许计数,检测是否小于9

ELSE Q:= (OTHERS=>'0');--大于9,计数值清零

END IF;

END IF;

END IF;

END IF;

IF Q = "1001" THEN COUT <= '1'; --计数大于9,输出进位信号

ELSE COUT<= '0';

END IF;

DOUT<=Q;--将计数值向端口输出

END PROCESS;

END behav;

实验内容Ⅱ:

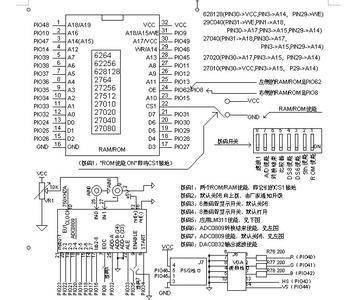

引脚锁定以及硬件下载测试。若选择目标器件是EP1C3,建议选实验电路模式5(具体电路图见说明书),用时钟CLOCK0(93引脚)接到CLK上,用键1(PIO0,引脚号为1)控制RST;用键2(PIO1,引脚号为2)控制EN;用键3(PIO2,引脚号为3)控制LOAD;用键4~7控制LOAD;输出数据DOUT接到数码管1上,PIO16~PIO19(引脚号为41~44);COUT接到PIO8(引脚号为11);最后进行编译、下载和硬件测试实验。

模式5:

结构图信号/与芯片引脚对照表

结构图上的信号名 | Cyclone系列的EP1C3TC144芯片引脚号 | 结构图上的信号名 | Cyclone系列的EP1C3TC144芯片引脚号 | 结构图上的信号名 | Cyclone系列的EP1C3TC144芯片引脚号 |

PIO0 | 1 | ||||

PIO1 | 2 | PIO31 | 72 | PIO71 | 119 |

PIO2 | 3 | PIO32 | 73 | PIO72 | 114 |

PIO3 | 4 | PIO33 | 74 | PIO73 | 113 |

PIO4 | 5 | PIO34 | 75 | PIO74 | 112 |

PIO5 | 6 | PIO35 | 76 | PIO75 | 111 |

PIO6 | 7 | PIO36 | 77 | PIO76 | 143 |

PIO7 | 10 | PIO37 | 78 | PIO77 | 144 |

PIO8 | 11 | PIO38 | 83 | PIO78 | 110 |

PIO9 | 32 | PIO39 | 84 | PIO79 | 109 |

PIO10 | 33 | PIO40 | 85 | SPEAKER | 129 |

PIO11 | 34 | PIO41 | 96 | CLOCK0 | 93 |

PIO12 | 35 | PIO42 | 97 | CLOCK2 | 17 |

PIO13 | 36 | PIO43 | 98 | CLOCK5 | 16 |

PIO14 | 37 | PIO44 | 99 | CLOCK9 | 92 |

PIO15 | 38 | PIO45 | 103 | ||

PIO16 | 39 | PIO46 | 105 | ||

PIO17 | 40 | PIO47 | 106 | ||

PIO18 | 41 | PIO48 | 107 | ||

PIO19 | 42 | PIO49 | 108 | ||

PIO20 | 47 | PIO60 | 131 | ||

PIO21 | 48 | PIO61 | 132 | ||

PIO22 | 49 | PIO62 | 133 | ||

PIO23 | 50 | PIO63 | 134 | ||

PIO24 | 51 | PIO64 | 139 | ||

PIO25 | 52 | PIO65 | 140 | ||

PIO26 | 67 | PIO66 | 141 | ||

PIO27 | 68 | PIO67 | 142 | ||

PIO28 | 69 | PIO68 | 122 | ||

PIO29 | 70 | PIO69 | 121 | ||

PIO30 | 71 | PIO70 | 120 |

(五)实验结果:

1.建立文件:

2.建立工程:

3.编译结果:开始出现几处标点错误,经改正,最终编译成功:

4.仿真结果:

5.引脚选择:CLK:引脚93.EN:引脚1.

RST:引脚2LOAD:引脚3

DATA[0]:引脚7.DATA[1]:引脚6.DATA[2]:引脚5.DATA[3]:引脚4.

DOUT[0]:引脚39.DOUT[1]:引脚40.DOUT[2]:引脚41.DOUT[3]:引脚42.

6.下载:

<1>打开编程窗口和配置文件。首先将适配板上的JTAG口和USB或并口通信线连接好,打开电源。在工程管理窗口选择ToolsProgrammer命令,在编程窗口的编程模式Mode中选择JTAG,并选中下载文件右侧的第一个小方框。如果此文件出现或有错,可单击左侧AddFile按钮,手动选择配置文件。

<2>.设置编程器:单击HardwareSetup按钮,在弹出的窗口中设置下载接口方式,这里选择US B-Blaster。向FPGA下载SOF文件前,要选择打钩。Program/Configure项。最后单击下载标符Start按钮,即进入对目标器件FPGA的配置下载操作。当出项“onfigurationSucceeded”时,表示编程成功。如图:

7.硬件测试:显示0-9,即十进制计数器,逢十进位灯闪烁一次,如下视频:

爱华网

爱华网