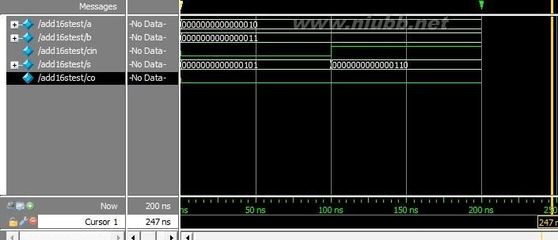

关于加法器的写法,网上有很多资料,原理什么的就不多说了,这里给出一个简单通用的8位超前进位加法器的模板,只求拿来就用^_^...module adder8 (//input:a,b,cin, //carry in//output:sum, //sum of a and bco //carry out);

input [7:0] a;input [7:0] b;input cin;output wire [7:0] sum;output wire co;

wire c0, c1, c2, c3, c4, c5, c6, c7, c8;wire g0, g1, g2, g3, g4, g5, g6, g7;wire p0, p1, p2, p3, p4, p5, p6, p7;wire s0, s1, s2, s3, s4, s5, s6, s7;

assign g0=a[0]&b[0];assign g1=a[1]&b[1];assign g2=a[2]&b[2];assign g3=a[3]&b[3];assign g4=a[4]&b[4];assign g5=a[5]&b[5];assign g6=a[6]&b[6];assign g7=a[7]&b[7];

assign p0=a[0]|b[0];assign p1=a[1]|b[1];assign p2=a[2]|b[2];assign p3=a[3]|b[3];assign p4=a[4]|b[4];assign p5=a[5]|b[5];assign p6=a[6]|b[6];assign p7=a[7]|b[7];

assign c0=cin;assign c1=g0|p0&c0;assign c2=g1|p1&c1;assign c3=g2|p2&c2;assign c4=g3|p3&c3;assign c5=g4|p4&am【】p;c4;assign c6=g5|p5&c5;assign c7=g6|p6&c6;assign c8=g7|p7&c7;

assign s0=a[0]^b[0]^c0;assign s1=a[1]^b[1]^c1;assign s2=a[2]^b[2]^c2;assign s3=a[3]^b[3]^c3;assign s4=a[4]^b[4]^c4;assign s5=a[5]^b[5]^c5;assign s6=a[6]^b[6]^c6;assign s7=a[7]^b[7]^c7;

assign sum = {s7,s6,s5,s4,s3,s2,s1,s0};assign co = c8;endmodule

总结: 原则上,本模块描述的加法器可以根据需要定义成16位等更高的位数,但是考虑到位数增加后,每根导线的扇出系数变得很大,所以如果需要更高位的加法器,可以用8位或者4位的超前进位加法器进行级联。

爱华网

爱华网