摘要:本论文的主要目的是通过研究深亚微米集成电路器件中栅氧化层可靠性,利用笔者所在公司不同技术代工艺制造的器件深入探讨栅氧的经时击穿行为(TDDB)及其损伤机理,从而探索器件栅氧化层退化规律,获得其有效寿命的精确测定。

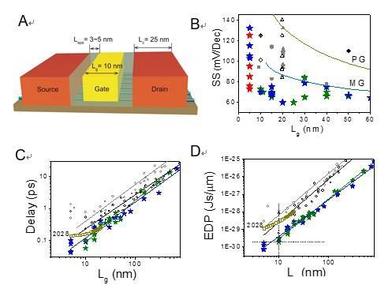

随着工艺技术的发展,器件的线宽不断缩小,使得芯片集成度上升,成本下降以及器件拥有较大的驱动电流。但随之而来的超薄氧化层所造成的漏电流的增加在可靠性方面产生了严重的问题。当器件沟道长度缩小至0.18μm,栅极氧化层在3 nm左右,此时器件栅氧化层的击穿机理已经与较厚氧化层器件的大不一样,外推获得氧化层寿命的经验模型是采用E模型还是1/E模型,都是目前普遍关注的问题。本文分析了上述两种模型各自的优缺点和适用范围,同时进行了大量实验测试,对汇集的数据进行了分析整理,发现了一些内在的特定的深层次机理,而这些机理是在目前国内国际同行研究结果所没有的。相信本论文能够给业界同行开展相关工作时提供明确信息,同时也希望引发更广泛、更深入的讨论,使得这一难题最终被完全解决。

关键词:TDDB;可靠性,F-N 隧穿电流;电荷泵

1引言

MOS晶体管中的栅氧化层是由硅衬底在高温下氧化形成的,这层SiO2膜是一种具有1015Ω・cm左右的高电阻率的绝缘膜,当外加电场大于6 MV/cm时,会产生Flowler-Nordheim(F-N)隧穿电流。随着超大规模集成电路的集成度不断提高,其MOS栅长已进入深亚微米阶段,作为介质层的栅氧化层厚度也不断减小。当前0.25μm工艺的栅氧化层厚度为4~5 nm,而如果到了0.18μm工艺时,栅氧化层的厚度将仅为2~3 nm。当电源电压为1.3 V时,二氧化硅膜上的电场就有大于6 MV/cm而产生击穿,从而必须考虑绝缘击穿对MOS氧化层质量的影响。绝缘击穿分为两种情况,一种是氧化层加上电压立即短路的瞬时绝缘击穿(Time-zero dielectric breakdown,TZDB);另一种是氧化层连续加上适当的电压后才产生短路的经时绝缘击穿(Time-dependence dielectric breakdown,TDDB)。相比较而言,TDDB作为一种主要的薄栅氧化层(厚度小于20 nm)质量评测方法在企业与实验室中得到了更为广泛的应用。

2MOS晶体管栅氧的可靠性

人们自70年代初开始研究TDDB的本征击穿机理,但是,真正能精确描述栅氧化层击穿的完整模型至今仍未找到,很多模型的物理机制仍与实验结果存在着矛盾。二十多年来人们提出了近10个模型试图解释栅氧化层的击穿,但最为流行的不外乎E模型和1/E模型。

在传统模型的运用中,我们发现,由于模型的实用性和局限性的影响,导致在真正栅氧评价中会碰到不少难题和需要修正的地方:

传统模型外推氧化膜寿命时需要大量测试,会消耗大量的成本和时间,必定会延缓技术、产品面世的时间,降低产品的竞争力,甚至会被淘汰,让所有产品开发的努力付诸东流。

传统模型只关注击穿时间分布,而不考虑TDDB过程特性,例如厚氧化膜在高电压状态下会经历一个隧穿电流很大,但仍然未击穿的状态,此时器件已经不可能正常工作,而传统模型不能外推这个状态。这是氧化膜电子运动规律造成的,因此需要新的模型准确刻画。

潜在突破点:在TDDB测试过程中,不同的氧化膜表现出来的测试曲线完全不同:厚栅氧会有一个波峰出现,然后Ig再慢慢变小,最后击穿(见图1);稍微薄一些的栅氧的Ig缓慢持续下降直至击穿(参见后面5 V栅氧TDDB测试);超薄的栅氧在TDDB测试过程中Ig缓慢增加直至击穿(见图2)。这些特征就是载流子在栅氧中竞争运动造成的,所以需要通过试验和研究来了解空穴和电子在氧化膜中碰撞产生电荷陷阱以及固定电荷的规律,分析不同技术代氧化膜击穿行为的不同点寻找潜在本质规律,挖掘栅氧化层随时间退化的内在物理机理。以上工作都需要通过更仔细的研究来获得氧化膜更准确的模型。

3不同技术代氧化膜的评价

3.1不同厚度NMOS栅氧击穿试验

试验水准如表1所示。本实验采用的仪器是HP4156B、HP4284、HP8110。

工作电压为5 V的MOS器件栅氧(155 ?�)进行V斜坡测试的击穿电压为-22 V,选用-19 V作为恒压做TDDB测量,并在应力分别施加0 s、1 s、3 s、5s、10 s、20 s、50 s、100 s、200 s、500 s、1000 s后测量其C-V特性曲线(频率1 MHz,交流幅值0.025 V)。工作电压为13.5 V的MOS器件栅氧(360 ?�)进行V斜坡测试的击穿电压为-41 V,选用-36.5 V作为恒压作TDDB测量,并在应力分别施加0 s、1 s、3 s、5 s、10 s、20 s、50 s、100 s、200 s、500 s、1000 s后测量其C-V特性曲线(频率10 kHz,交流幅值0.025 V,),观察氧化膜内部缺陷的状态变化。它们的测量结果如图4(a),图4(b)和图5(a),图5(b)所示。

工作电压为5 V的MOS器件栅氧(155 ?�)进行V斜坡测试的击穿电压为-22 V,选用-19 V作为恒压做TDDB测量,并在应力分别施加0 s, 1 s、3 s、5s、10 s、20 s、50 s、100 s、200 s、500 s、1000 s后测量其C-V特性曲线(频率1 MHz,交流幅值0.025 V)。工作电压为13.5 V的MOS器件栅氧(360 ?�)进行V斜坡测试的击穿电压为-41 V,选用-36.5 V作为恒压作TDDB测量,并在应力分别施加0 s、1 s、3 s、5 s、10 s、20 s、50 s、100 s、200 s、500 s、1000 s后测量其C-V特性曲线(频率10 kHz,交流幅值0.025 V,),观察氧化膜内部缺陷的状态变化。它们的测量结果如图3(a),图3(b)和图4(a),图4(b)所示。

我们从C-V及CP曲线上可看出:

由于高应力对氧化膜1 s的损坏,让C-V的Cmin迅速向右移动,将让该栅氧的NMOS Vt C-V曲线底部变得平坦,主要是由于大量界面态的产生,而之后平坦程度不再大幅度增加,说明界面态在应力刚开始施加阶段就基本产生。这一点我们也可以从CP曲线得到证明:Icp的峰值在1 s内提高了2个数量级。

C-V及CP曲线的左右移动,表面内部正负电荷有一个竞争的过程,导致内部电场发生改变。

由于两种氧化膜的上电极都是同等掺杂浓度的N+多晶硅,下电极是P阱,所以功函数一致,因此Vfb大约都是1.2 V左右。

从C-V曲线上还可以看出该栅氧对应的NMOS晶体管的Vt即C-V曲线的最低点,当加了负的应力后,初始阶段Vt变成负的,NMOS晶体管变成一个耗尽型晶体管。

随着氧化膜的增厚,Dit饱和所需要的时间也增加,数量也更多,但在最后都趋于饱和,见图3(d)和图4(d),所以反映在器件上面就是Vt、开态电流Ion、跨导Gm的漂移量也会趋于饱和。

3.2 新的机理模型――内建电场模型

在大量的工作实践中,我们发现E模型和1/E模型在计算氧化膜寿命时,只是对最终的氧化膜寿命有一个统计的分析,对于在氧化膜使用过程中电荷积累的中间状态不能描述;而现在急切需要一种新的模型,能够定性地刻画氧化膜在应力状态下的漏电状态、界面态密度和电荷陷阱,从而让我们能更深刻地认识氧化膜损伤的过程。

如图5所示,对于一般的NMOS栅氧(厚度360 ?�左右),在TDDB测试中在栅端加负偏压,P型衬底一侧的能带下移,外电场方向由衬底指向N+多晶硅栅:

如图5(a), 在此电场驱动下,电子从N+多晶硅栅注入栅氧,这时由于F-N和直接隧穿同时存在,而F-N占主导作用,电子的高迁移率和低跃迁能的特性,使得部分电子在氧化膜中被陷阱俘获后又激发,比较难被阴极端的陷阱完全俘获,最后到达P型衬底形成电子电流;而P型衬底端的多子空穴也在电场作用下部分注入栅氧中,由于空穴有效质量比电子大很多,而且陷阱一般聚集在Si-SiO2界面处,所以空穴非常容易被俘获而停留在栅氧靠近衬底方向。

如图5(b), 由于陷阱不断俘获空穴,使得靠近P型衬底的能带下凹,在靠近栅极区域的氧化膜内部形成一个与外电场同向的电场,使得该区域电场强度增大,电子更容易穿过栅氧。反映在TDDB上为开始时期Ig慢慢变大。

如图5(c), 但是由于越来越多的电子在电场作用下从栅极到衬底输运的过程中被P型衬底附近栅氧中的界面态俘获,这样慢慢抑制了以前由于空穴的内建电场,直至内建电场反向,靠近栅极区域的氧化膜内部形成一个与外电场反向的电场,使得该区域电场下降。电子在靠近衬底的栅氧中被俘获,造成该区域的能带上鼓。宏观反映为Ig达到一个峰值后慢慢变小。

如图5(d), 由于电子在靠近衬底的栅氧内不断积累,并慢慢向栅极方向的陷阱推进,靠近栅极区域的氧化膜内部电场下降更厉害,反映在宏观上Ig变得更小,但慢慢饱和;最后栅氧中陷阱的增多形成了通路,这时候栅氧被击穿。因此Ig 是电子电流和空穴电流的线性叠加的结果。

对于PMOS栅氧只需要将图5中能带更改方向即可作为参考研究。

4小结

我们从栅氧可靠性评价测试方法开始,对可靠性评价的测试方法进行了逐一介绍,随后我们对不同技术代氧化膜进行了详细的评价(包括高低温测试、不同应力测试、N型P型栅氧测试),最后根据评价结果定性的推出了新的内建电场机理模型。

致谢

笔者衷心感谢华虹NEC-TD相关同事的大量实验工作支持,感谢华虹NEC-QA部门技术工程师们数据分析与有益探讨。

参考文献

[1] M. Renovell, J.M. Galliere, F. Azais, and Y. Bertrand,European Test Workshop, pp.75-80, 2002.

[2] R. Degraeve, B. Kaczer, A. De Keersgieter, and G.Groeseneken, Reliability Physics Symposium, 2001.Proceedings. 39th Annual. 2001 IEEE International, pp. 360-366, 2001.

[3] J.M. Soden, and C.F. Hawkins, Design & Test ofComputers, pp. 56-64, 1986.

[4] J. Segura, J. Figueras, and A. Rubio, Microeletron. Reliab.,Vol. 32, No. 11, pp. 1509-1514, 1992.

作者简介

董科,八年以上逻辑,HV, BCD以及可靠性相关研发项目管理经验,现任华虹NEC技术开发部BCD工艺集成经理。

百度搜索“爱华网”,专业资料、生活学习,尽在爱华网!

爱华网

爱华网