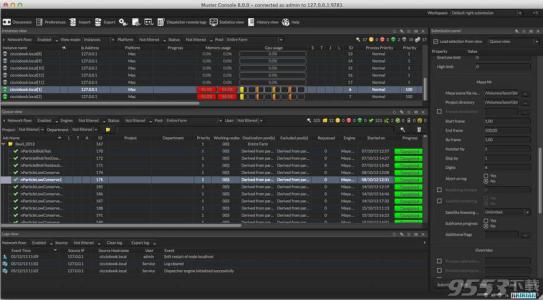

vertex_vertex -简介

Virtex是Xilinx FPGA中的高端产品,占据着全球高端产品的大部分市场,从Virtex-II开始,这一系列产品不断升级和更新,性能也越来越卓越。Xilinx于2011年推出了最新的Virtex-7。vertex_vertex -资源

以Virtex-II为例说明器件结构及内部资源。Virtex-II内部资源包括RAM,乘法器,IOB,可编程互联线,数字时钟管理器DCM和可编程逻辑阵列CLB。CLB: 每个CLB包括开关阵列、 4个slice、两条单独的进位链及本地布线资源。slice包含了基本的逻辑单元,开关阵列用于同基本的布线资源相连接,本地互联线用于连接内部slice以及相邻CLB中的slice。

slice:slice是XilinxFPGA中的基本逻辑单元,在一般的设计中,逻辑资源的使用情况用已使用的slice的个数来衡量。每个slice包括两个四输入查找表(LUT)、一条进位链以及两个寄存器,还包括一些多路选择器。

multiplier:乘法器输入位宽为18bit,输出36bit,每个18*18的乘法器可作为2个9*9乘法器使用。在芯片内部,乘法器和内嵌RAM是相邻的。

IOB:输入:2个DDR寄存器。输出:2个DDR寄存器、两个3态使能DDR寄存器。输入输出有单独的时钟和使能,共享复位和置位信号。提供可选的电平标准: LVTTL, LVCMOS (3.3V, 2.5V, 1.8V,1.5V)、 PCI-X (133 MHz)PCI (3.3V 33 MHz & 66 MHz)、GTL、GTLP等。RAM:双端口RAM,每个端口拥有同步的读写使能,两个端口有使用单独的时钟,在器件内部,RAM与乘法器相邻,以获得更高速度。

DCM:每个器件多达12个DCM,分布在顶部和底部的边缘,提供DLL,DFS,DPS。DCM输出能直接驱动互联线。

爱华网

爱华网