采用4位超前进位加法器与门电路的组合、4位超前进位加法器与数据比较器的组合两种方法设计两位十进制加法器的实验电路,为学生在数字电路实验中提供十进制加法的电路。

十进制加法器_十进制加法器 -解释

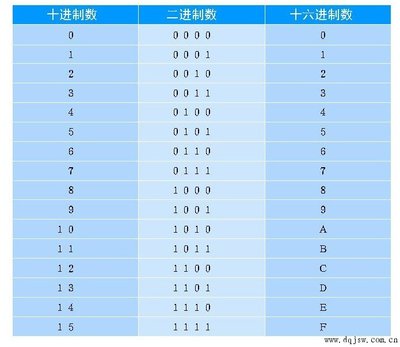

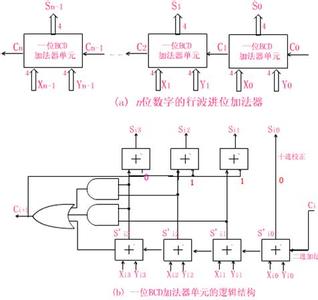

十进制加法器可由BCD码(二-十进制码)来设计,它可以在二进制加法器的基础上加上适当的“校正”逻辑来实现,该校正逻辑可将二进制的“和”改变成所要求的十进制格式。n位BCD码行波式进位加法器由n级组成,每一级将一对4位的BCD数字相加,并通过一位进位线与其相邻级连接。在十进制运算时,当相加二数之和大于9时,便产生进位。可是用BCD码完成十进制数运算时,当和数大于9时,必须对和数进行加6修正。这是因为,采用BCD码后,在二数相加的和数小于等于9时,十进制运算的结果是正确的;而当相加的和数大于9时,结果不正确,必须加6修正后才能得出正确的结果。

十进制加法器_十进制加法器 -相关条目

电脑科技语言

爱华网

爱华网